随着集成电路的制造工艺逐渐达到了硅材料本身的物理极限,新型二维原子晶体材料(简称二维材料),例如二硫化钼(MoS2)和二硫化钨(WS2)等硫族化合物,基于其具原子级别厚度、表面天然钝化、能够与标准半导体工艺兼容的优势,2020年开始,半导体主要玩家台积电、英特尔、三星以及创新技术策源欧洲地欧洲微电子研究中心IMEC,都已经大力布局二维材应用的二维材料研究成果并将其列为未来1纳米节点后晶体管技术的最重要方案。

近年来,二维材料的研究重点开始从基础研究逐渐向工程实际应用转移。大面积的材料生长也获得了突破,然而基于二维材料体的集成电路发展仍处于起步阶段,如何针对二维材料进行器件工艺和电路设计的定制优化是目前面临的主要。此外,由于二维硫族化合物中存在硫属元素空位,通常表现出N型半导体特性,目前为止报道的二维材料电路也主要基于典型的伪NMOS结构,与互补型的CMOS技术相比,伪NMOS集成电路有对晶体管均一性要求高、功耗较高等缺点。所以亟需寻找一种适合二维材料的电路架构。

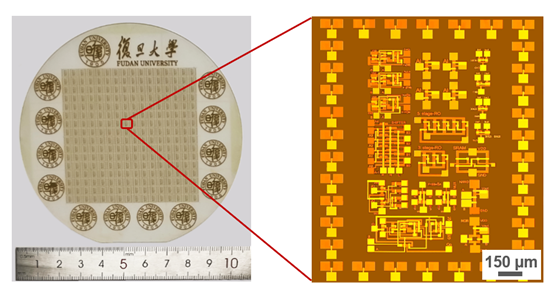

近日,复旦大学微电子学院包文中课题组及其合作者,基于有实用化价值的4英寸单层MoS2晶圆,成功实现了低功率互补传输晶体管逻辑(CPL)电路结构。CPL结构属于传输管逻辑的一种,它由互补输入/输出、NMOS传输晶体管逻辑网络和输出反相器组成,可以在单极性晶体管的基础上优化电路面积并兼具CMOS的低功耗优势。该工作基于顶栅结构的二维MoS2场效应晶体管,对阈值电压和载流子迁移率等关键器件参数进行了协同优化。首先制造并测试了基本的反相器、静态随机存取存储器和环形振荡器,验证了二维电路集成工艺的可靠性。然后设计并实现了基于CPL结构的功能逻辑单元(AND/NAND、OR/NOR、XOR/XNOR、1位全加器),还进一步制备了CPL架构的数据选择器(MUX)、多路分解器(DEMUX)和左右移位器(SHIFTER)。这项工作展示了二维材料在集成电路中的实用化价值,并展示了复杂二维电路设计的潜力。

文章以“Pass-transistor Logic Circuits Based on Wafer-Scale Two-Dimensional Semiconductors”为题发表在期刊Advanced Materials上。复旦大学微电子学院硕博生王馨雨、陈新宇、马静怡为第一作者,复旦大学包文中研究员为该系列工作的主要通讯作者,复旦大学微电子学院包文中研究员、解玉风教授,以及复旦大学芯片与系统前沿技术研究院边历峰研究员为共同通讯作者。该工作得到了科技部重点研发计划纳米前沿专项、国家自然科学基金,上海市科委以及张江复旦国际创新中心集成电路创新平台的支持。

文章链接:https://onlinelibrary.wiley.com/doi/10.1002/adma.202202472