二维半导体是集成电路工艺发展到1 nm节点最受关注的新路径。虽然国际工业界认为引入二维半导体可以在CMOS平面工艺中有效解决晶体管尺寸缩放过程中的问题,但其重要发展瓶颈之一在于需要提供高质量、快速生产的大规模晶圆。迄今为止,世界上主要的头部企业例如英特尔,三星,台积电和欧洲的IMEC研发中心都在二维半导体上投入了大量资源,并积极引入国际领军团队。当前研究人员开发了多种策略来制备大面积二维半导体,其中化学气相沉积(CVD)是普遍看好的技术。但是主要研究更多注重实验室级别的性能(Performance)提升,并没有充分考虑材料生长的规模(Scale)和成本(Cost)。

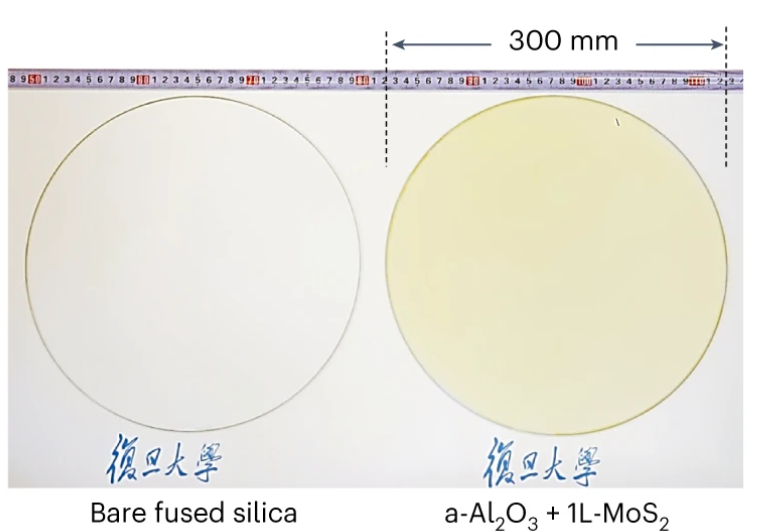

复旦大学周鹏-包文中团队取得重大研究进展,发明了一种面向集成电路制造的二维材料生长方法,能够在工业界主流12英寸(300毫米)晶圆上进行均匀和单层材料的快速生长,相关成果以“12-inch growth of uniform MoS2 monolayer for integrated circuit manufacture”为题发表于国际顶级期刊《自然·材料》(Nature Materials)。这项工作不仅提供了二维材料CVD生长的新思路,实现了从0到1的突破;同时也聚焦二维半导体的集成电路应用,充分考虑了规模-成本-性能(S-C-P)指标的协同优化,着眼于从1到10的转化。

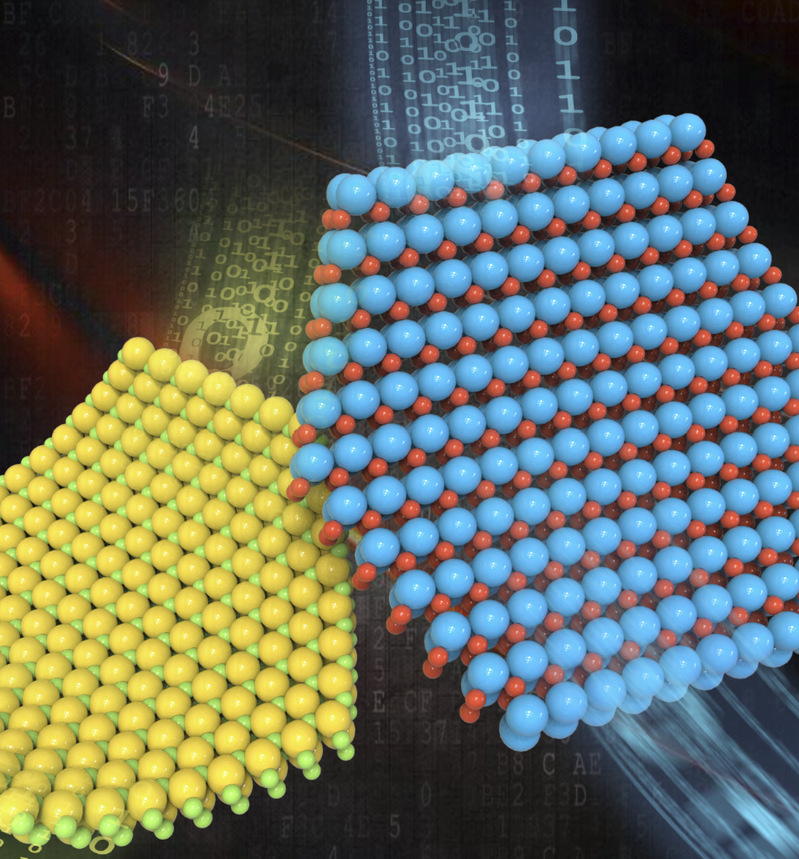

传统二维材料CVD生长的难点在于原子级的精准可控与批次重复性,这需要对诸多控制参数进行协同优化,包括生长衬底的特殊处理。此成果开创性的采用了海绵缓释结构的前驱体设计,以及流体动力学优化的多硫源分布,从而实现了二维材料的准静态生长;同时在任意衬底(包括硅)通过原子层沉积生长特殊缓冲层,精确控制均匀单层成核,最终获得了大面积二维半导体均匀生长技术,并且对于多种二维半导体均可适用,在15分钟就可快速实现12英寸晶圆内低缺陷的二维单层全覆盖。得益于能够在任意衬底上进行生长,研究者还展示了绝缘体上硅(SOI)的晶圆结构流程制作晶体管阵列,避免了复杂转移方法。本成果展示的绝缘体上二维材料(2D-OI)具有原子级的半导体沟道,在先进制程中可以充分发挥二维半导体的优势。此外材料表征结果证明,生长的二维薄膜晶粒间有着良好的原子级拼接,在室温下二维晶体管的电学性能和晶粒大小、多晶晶界并没有直接关联,统计结果显示了优异的器件电学均一性。这些发现为二维半导体提供了从实验室向产业界过渡的发展路径。

该工作得到了复旦大学张江国际创新中心、国家自然科学基金委,上海市科学技术委员会,国家重点研发项目资助。

文章链接: https://www.nature.com/articles/s41563-023-01671-5

本新闻稿转载自复旦大学微电子学院新闻,原文链接: https://mp.weixin.qq.com/s/KNkjQc8shEf9BEL0gJnvhg