当前,越来越多的半导体人士开始关注二维半导体。这种新型材料具有天然的原子级厚度,可以有效抑制短沟道效应,同时无悬挂键的完美表面和合适的能带结构能够让电子在晶体管沟道中更快的运行。这些特性使其成为探索未来面向集成电路1 nm以下先进技术节点的最合适材料体系。

近年来大面积二维半导体的生长已经取得了显著进展,包括晶圆级MoTe2和MoS2的生长,这解决了二维材料大规模应用的材料难题;同时,二维半导体基础器件的研究也取得诸多进展,包括超短沟道、超低接触电阻的MoS2、InSe等弹道输运晶体管,报道的器件性能也大幅超越了相同尺寸的硅基器件。值得注意的是,近年来越来越多基于二维半导体的中等规模集成电路成果开始涌现,说明这个领域已经开始逐步向工业级应用发展。

在向产业化技术演进中,二维半导体与成熟硅基CMOS工艺的深度融合也已成为学术界和业界关注的焦点。当前技术发展面临的核心挑战在于异质材料集成方案的工艺兼容性问题:主流二维CMOS反相器普遍采用异质材料体系通过转移方法构建P/N沟道,其复杂的转移工艺与现有硅基工艺存在显著差异,导致器件良率难以突破工业化量产阈值。然而完全沿用传统CMOS工艺也有困难:传统离子注入掺杂技术在原子层厚度的二维材料体系中面临严峻挑战——高能离子轰击易造成二维材料晶格损伤,导致载流子迁移率显著降低。

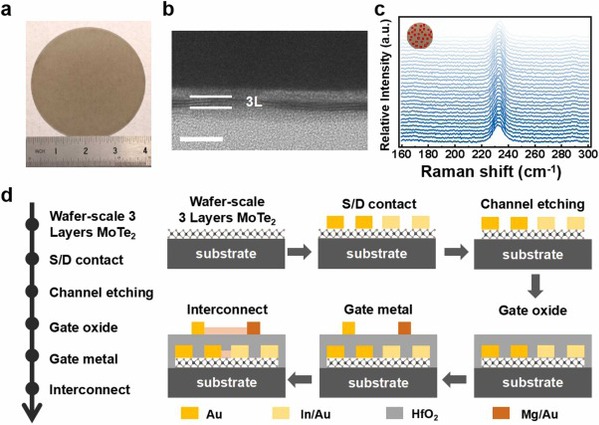

复旦大学微电子学院包文中研究员和材料系李文武研究员,针对这一技术瓶颈合作研发,通过借鉴硅基CMOS器件的设计理念,重点突破原子层精准掺杂、二维CMOS器件工艺协同优化等工艺瓶颈问题,首次提出了基于二维同质MoTe2非破坏性掺杂的二维CMOS单片集成工艺,成功实现了4英寸晶圆级二维 CMOS的单片集成,并且展现了良好的工艺兼容性。展示的二维CMOS反相器阵列电压增益可以达到35。这项工作为未来晶圆级二维CMOS集成电路的实现提供了可行的解决方案。文章以“First demonstration of monolithic CMOS based on 4-inch three-layer MoTe2”为题发表在期刊Materials Science and Engineering: R: Reports上。博士研究生胡焱、盛楚明为本文第一作者;复旦大学包文中研究员、李文武研究员,六碳科技创始人许子寒为共同通讯作者。该研究得到了国家重点研发计划、上海市科学技术委员会、上海市基础研究试点项目、国家自然科学基金、教育部创新平台青年科学家项目的支持。

该研究通过二维原子层精准掺杂、接触和顶栅工艺的协同优化,首次实现了基于顶栅器件结构的4英寸晶片级3层MoTe2 CMOS反相器的单片集成。未来,单片集成二维CMOS技术的实际产业化应用道路仍存在性能提升、工艺协同优化、制造良率提升、热预算控制等关键问题亟待攻克,但该领域的技术突破将为延续摩尔定律提供全新思路和解决方案。

文章链接:https://doi.org/10.1016/j.mser.2025.100938