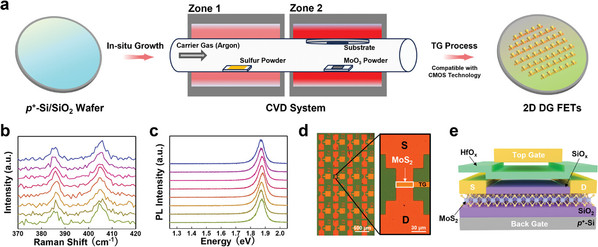

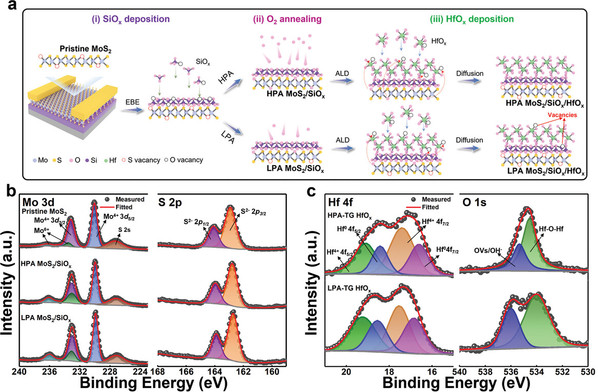

该工作通过依次在单层MoS2表面堆叠完全来源于CMOS技术的介质材料SiOx和HfOx,从而在二维材料的无悬挂键表面实现高k介质集成;随后,沉积顶栅电极Au,器件整体形成不对称双栅结构。通过进一步对缺陷分布所造成的器件电学性能差异的研究发现,背栅模式下(顶栅接地),器件由于介质层覆盖效应和采用顶栅调制策略,可同时实现精确的n型/p型掺杂效果。顶栅模式下(背栅接地),所沉积的混合介质作为器件栅介质层,极大改善了器件的电学性能调控;但受缺陷分布影响,采用不同工艺的器件呈现出差异明显的小回滞或较大回滞。双栅模式进一步优化器件综合性能,随着VBG从0增加到+40 V,迁移率(μ)从36.9增加到65.7 cm2 V-1 s-1。此外,由于精良的后栅极工艺,所制备的光电晶体管都展现出较高光响应度以及优异的探测率。

该工作所提出的后栅极集成方法与传统硅CMOS技术完全兼容,由于解决了无悬挂键表面难以沉积高k介质的问题,因此也具有扩展到其他二维半导体材料中应用的前景。此外,该工作为二维半导体器件未来从实验室研究顺利过渡到规模化、工程化应用提供了切实可行的有效方法。文章以“Synergistic Engineering of Top Gate Stack for Low Hysteresis Two-Dimensional MoS2 Transistors”为题发表在著名期刊Advanced Functionals Materials上。博士生盛楚明为本文第一作者;包文中研究员,周鹏教授为共同通讯作者。该研究得到了国家重点研发计划、上海市基础研究试点项目(复旦大学)、教育部创新平台青年科学家项目的支持。

近日,复旦大学微电子学院包文中和周鹏教授团队,提出了一种基于单层MoS2的全CMOS兼容后栅极集成方法,可有效应用于小回滞、高稳定性的双栅晶体管及高性能封装沟道结构的光电晶体管制备。

该工作通过依次在单层MoS2表面堆叠完全来源于CMOS技术的介质材料SiOx和HfOx,从而在二维材料的无悬挂键表面实现高k介质集成;随后,沉积顶栅电极Au,器件整体形成不对称双栅结构。通过进一步对缺陷分布所造成的器件电学性能差异的研究发现,背栅模式下(顶栅接地),器件由于介质层覆盖效应和采用顶栅调制策略,可同时实现精确的n型/p型掺杂效果。顶栅模式下(背栅接地),所沉积的混合介质作为器件栅介质层,极大改善了器件的电学性能调控;但受缺陷分布影响,采用不同工艺的器件呈现出差异明显的小回滞或较大回滞。双栅模式进一步优化器件综合性能,随着VBG从0增加到+40 V,迁移率(μ)从36.9增加到65.7 cm2 V-1 s-1。此外,由于精良的后栅极工艺,所制备的光电晶体管都展现出较高光响应度以及优异的探测率。

该工作所提出的后栅极集成方法与传统硅CMOS技术完全兼容,由于解决了无悬挂键表面难以沉积高k介质的问题,因此也具有扩展到其他二维半导体材料中应用的前景。此外,该工作为二维半导体器件未来从实验室研究顺利过渡到规模化、工程化应用提供了切实可行的有效方法。文章以“Synergistic Engineering of Top Gate Stack for Low Hysteresis Two-Dimensional MoS2 Transistors”为题发表在著名期刊Advanced Functionals Materials上。博士生盛楚明为本文第一作者;包文中研究员,周鹏教授为共同通讯作者。该研究得到了国家重点研发计划、上海市基础研究试点项目(复旦大学)、教育部创新平台青年科学家项目的支持。