摘要

复旦大学包文中研究员等人发表了题为“ High-linearity flash ADC achieved through design-technology co optimization based on two-dimensional semiconductor的工作于Science Bulletin期刊上。该工作通过设计-工艺协同优化(DTCO)策略,成功研制出基于二维半导体的3位Flash模数转换器(ADC),实现了超高线性度和超低功耗。该ADC通过优化材料、制造工艺和电路设计,显著降低了非线性误差,实现了差分非线性(DNL)为0.072 LSB、积分非线性(INL)为0.128 LSB,同时保持了极低的功耗(3.36μW)。这些成果为二维半导体在高级信号处理中的应用提供了宝贵的见解和技术路径。

背景

随着物联网(IoT)的快速发展,智能设备对集成模数转换器(ADC)的需求急剧增加,尤其是在低功耗和高稳定性方面。尽管传统的硅基ADC取得了显著进展,但在微型化、可穿戴性和能效方面仍面临挑战。近年来,二维半导体(2DSCs)因其原子级厚度和优异的电学性能,在低功耗电路和柔性电子领域受到广泛关注。然而,将2DSCs集成到模拟电路中面临诸多挑战,尤其是在复杂的混合信号电路中。本文通过设计-工艺协同优化(DTCO)策略,成功开发了一种基于2DSCs的3位Flash ADC。

主要内容

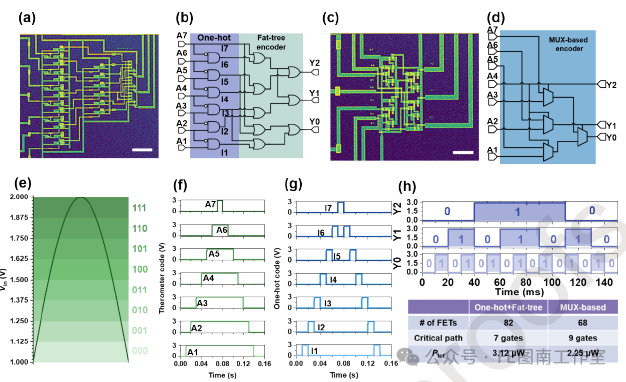

本文通过设计-工艺协同优化(DTCO)策略,成功开发了一种基于二维半导体的3位Flash ADC。研究者首先通过化学气相沉积(CVD)技术在4英寸蓝宝石基底上合成了单层二硫化钼(MoS2),并利用干法转移技术将MoS2堆叠在SiO2/Si基底上。通过优化接触结构,显著提高了器件的线性和电路的操作速度。研究者采用了退火工艺来最小化性能波动,确保长期运行的可靠性。在设计阶段,对模拟和数字模块进行了精心的结构选择和适配。通过离散时间比较器设计,有效减轻了工艺变化的影响。这种全面的协同优化策略,涵盖了材料选择、工艺改进和电路设计,确保了ADC的稳定性和精度。与使用微米级非硅基TFT工艺的ADC电路相比,开发的电路展现出更小的非线性误差,实现了有效的位数(ENOB)为2.6,并保持了极低的功耗(3.36μW)。

实验细节

实验中,研究者首先通过化学气相沉积(CVD)技术在4英寸蓝宝石基底上合成了单层MoS2。然后,利用激光直写技术对源极和漏极接触区域进行图案化,并通过CF4刻蚀去除接触区域的MoS2。接着,通过电子束蒸发技术沉积35nm厚的金层形成接触。MoS2通道通过CF4刻蚀定义,随后通过原子层沉积(ALD)技术形成20nm厚的高介电常数HfO2层。通过额外的光刻/剥离/沉积工艺周期,创建了顶部栅金属层(35nm金)。对于顶接触晶体管,制造过程与上述过程基本一致,但在光刻定义源极和漏极区域后,不需要刻蚀掉MoS2,而是直接沉积金属层形成源极和漏极电极。通过感应耦合等离子体刻蚀技术形成通孔,连接底层金属M0和金属M1层。对于独立的比较器和编码器,只需要满足测试需求的M1层。完整的ADC电路测试需要将互连层扩展到M2层,并通过物理气相沉积(PVD)技术生长SiO2实现互连层之间的隔离。M2金属互连和通孔到M2的制造过程与M1互连和通孔到M1的制造过程类似。

创新点

设计-工艺协同优化(DTCO):通过优化材料、制造工艺和电路设计,显著降低了ADC的非线性误差,实现了DNL为0.072 LSB、INL为0.128 LSB。

边缘接触结构:通过边缘接触结构显著提高了器件的线性和电路的操作速度,与顶接触结构相比,边缘接触结构展现出更低的亚阈值摆动(SS)和漏致势垒降低(DIBL)。

离散时间比较器:通过离散时间比较器设计,有效减轻了工艺变化的影响,提高了ADC的稳定性和精度。

低功耗设计:实现了极低的功耗(3.36μW),适用于低功耗应用。

结论

本文通过设计-工艺协同优化(DTCO)策略,成功开发了一种基于二维半导体的3位Flash ADC,实现了超高线性度和超低功耗。该ADC通过优化材料、制造工艺和电路设计,显著降低了非线性误差,实现了差分非线性(DNL)为0.072 LSB、积分非线性(INL)为0.128 LSB,同时保持了极低的功耗(3.36μW)。这些成果为二维半导体在高级信号处理中的应用提供了宝贵的见解和技术路径。

结果与讨论

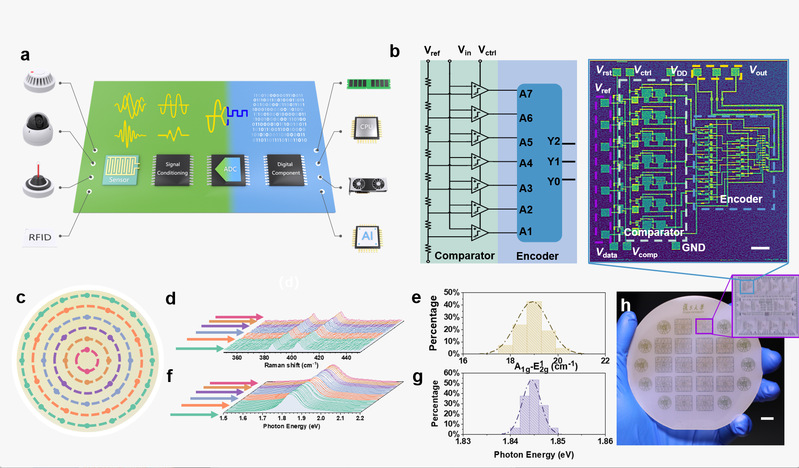

图1 基于4英寸晶圆级MoS2的ADC制备。(a)ADC模数转换功能示意图。(b)3位2D Flash ADC的电路图和SEM图像。伪彩色SEM图像显示了ADC测试所需的信号端口:Vctrl(用于切换比较器工作状态的控制信号)、Vrst(比较器复位阶段的输入控制信号)、Vcomp(比较器比较阶段的输入控制信号)、Vdata(待量化的输入信号)、Vref(参考电压)、VDD/GND(电源)、Vout(ADC输出)。(c)4英寸MoS2晶圆上材料表征选点示意图。(d)选定点的拉曼光谱。(e)拉曼光谱中E1 2g和A1g峰差值的直方图和高斯拟合。(f)选定点的光致发光(PL)光谱。(g)PL光谱峰值位置的直方图和高斯拟合。(h)制备的包含2D ADC电路的晶圆。比例尺:200微米(b)、20毫米(c)、1厘米(h)

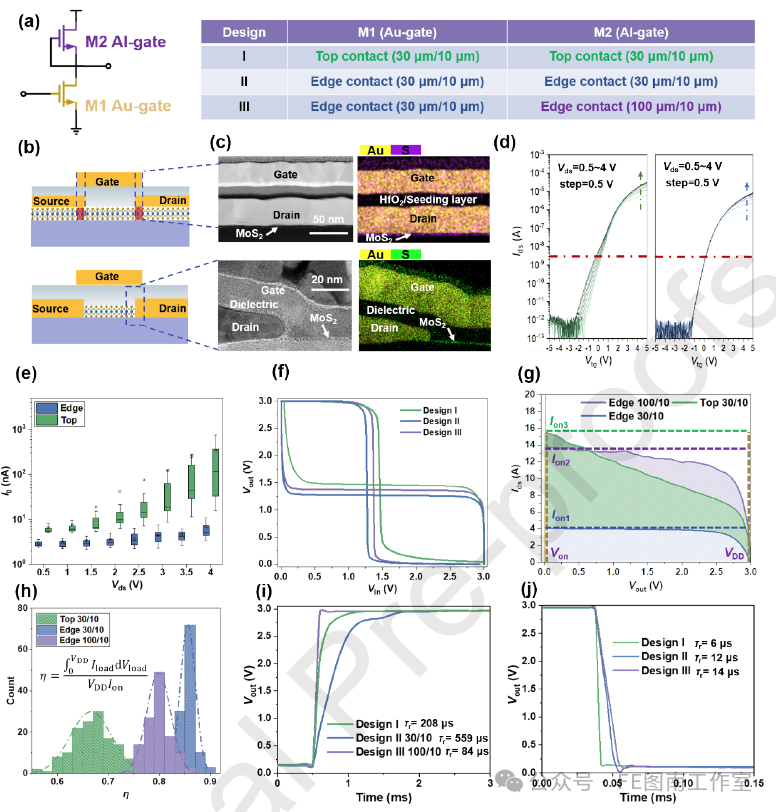

图2 MoS2反相器的设计技术协同优化(DTCO)方法。(a)NMOS反相器结构及三种设计方案的示意图。(b,c)顶部接触和边缘接触的晶体管结构示意图(b),以及局部TEM图像和EDS能谱(c)。(d)不同Vds下顶部接触和边缘接触Al栅晶体管的转移特性。(e)不同Vds下顶部接触和边缘接触Al栅晶体管在Vgs=0时的电流(I0)。(f)三种反相器设计的电压传输特性(VTC)曲线。(g)三种反相器设计的负载特性。(h)三种反相器设计η值的统计结果。(i,j)三种反相器设计的瞬态测试结果,包括上升时间(i)和下降时间(j)。

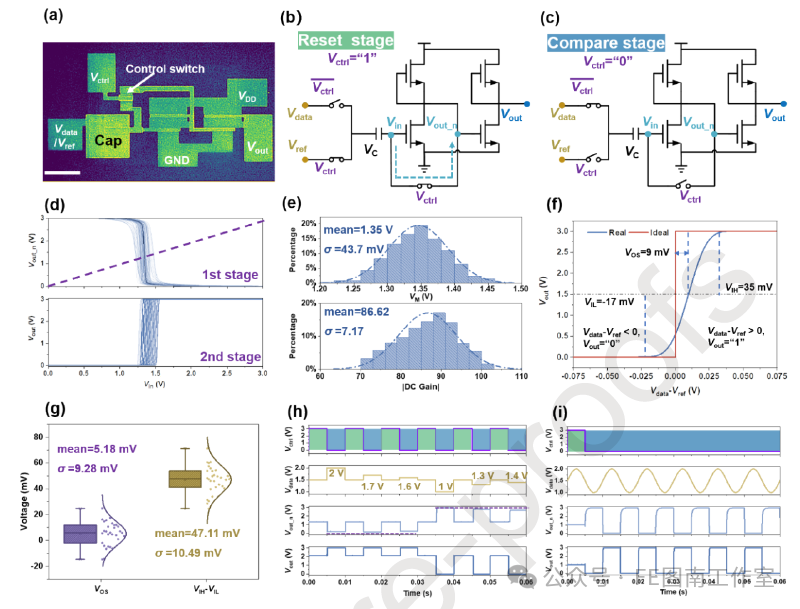

图3 离散时间比较器。(a)离散时间比较器的伪彩色SEM图像。(b,c)离散时间比较器电路结构示意图:复位状态(b)和比较状态(c)。(d)第一级和第二级反相器的电压传输特性曲线。(e)单级反相器的开关电压VM和直流增益统计值。(f)离散时间比较器的静态输出特性与理想比较器输出特性的对比。(g)离散时间比较器的最小可分辨电压差和输入失调电压Vos的统计结果。(h,i)比较器的动态测试结果:离散时间比较(h)和连续比较(i)。(a)比例尺为100微米。

图5 二维ADC的性能表现。(a)二维ADC的测试硬件平台,包含用于生成参考电压的DAC和用于施加控制信号的FPGA。(b)3位二维Flash ADC对正弦波信号的量化输出。(c)ADC的静态传输曲线。(d)通过ADC正弦波直方图测试获得的各码值出现频率。(e)3位二维Flash ADC的差分非线性(DNL)和积分非线性(INL)。(f)ADC输出的FFT频谱及其动态性能参数。

https://doi.org/10.1021/acsnano.5c11504